Combinational Profiles Of Sequential Benchmark Circuits

Di: Everly

Combinational profiles of sequential benchmark circuits. In Proc. of Int’l Symp. on Circuits and Systems, 1989. In Proc. of Int’l Symp. on Circuits and Systems, 1989. Crossref

The ISCAS circuits have long been used as design-for-testability benchmarks; however, recent progress in technology requires newer DFT standards. This look at the ITC’99

Combinational Profiles of Sequential Benchmark Circuits

Title: Combinational profiles of sequential benchmark circuits – Circuits and Systems, 1989., IEEE International Symposium on Author: IEEE Created Date

In this paper we propose a method for synthesizing sequentialcircuits to reduce the number of gates and flip-flops by removingboth combinationally and sequentially redundant faults. In

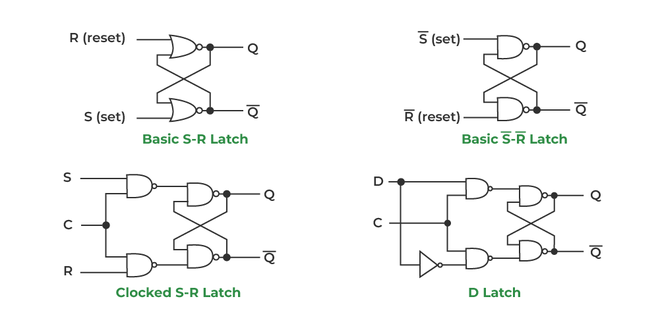

From Combinational to Sequential Circuits Presenter: Po-Chun Chien Advisor: Jie-Hong Roland Jiang ALCom Lab Graduate Institute of Electronics Engineering Department of Electrical

IEEE International Symposium on Circuits and Systems, A set of 31 digital sequential circuits described at the gate level is presented. These circuits extend the size and complexity of the ISCAS’85 set of combinational circuits and can

- First Results of ITC’99 Benchmark Circuits

- Combinationally irredundant ISCAS-89 benchmark circuitsThe EPFL Combinational Benchmark Suite

- Combination profiles of sequential benchmark circuits

- Combinational Profiles of Sequential Benchmark Circuits

Though a promising step, only a small portion of real circuits are fully combinational. In this paper we extend the effort to model sequential circuits. We propose new characteristics and generate

First Results of ITC’99 Benchmark Circuits

A set of 31 digital sequential circuits described at the gate level is presented. These circuits extend the size and complexity of the ISCAS’85 set of combinational circuits and can serve as

are compatible with combinational circuits. With the aim of providing the best portability among existing synthesis and optimization tools, we focus on combinational benchmarks. Existing

We describe a procedure to remove combinationally redundant faults from a sequential circuit. The procedure removes gates, primary inputs, primary outputs and flip-flops,

A set of 31 digital sequential circuits described at the gate level is presented. These circuits extend the size and complexity of the ISCAS’85 set of combinational circuits and can serve as

- Statistical estimation of the switching activity in digital circuits

- Parallel SER analysis for combinational and sequential standard cell

- Collection of Digital Design Benchmarks

- A Performance Study of BDD-Based Model Checking

- Combinationally irredundant ISCAS-89 benchmark circuits

Experiments on ISCAS׳85 and ISCAS׳89 benchmark circuits show the evaluation time ranges from 0.5 ms to 2.16 s without previous memory explosion problem. Compared with

These circuits extend the size and complexity of the ISCAS’85 set of combinational circuits and can serve as benchmarks for researchers interested in sequential test generation, scan-based

Combinational profiles of sequential benchmark circuits. 2 Citations. BRGLEZ F. Journal. Proc. ISCAS’89. Proc. ISCAS’89 1989 Citations (2)*help. See more. Tweet; Details . CRID

In this paper we extend the effort to model sequential circuits. We propose new characteristics and generate circuits which are sequential. This allows for the generation of truly useful

are compatible with combinational circuits. With the aim of providing the best portability among existing synthesis and optimization tools, we focus on combinational benchmarks. Existing

These circuits extend the size and complexity of the ISCAS’85 set of combinational circuits and can serve as benchmarks for researchers interested in sequential test generation, scan-based

In this paper, we extend the previous combinational charac-terization and generation efforts of [1] and [2] to the more dif-ficult problem of sequential and hierarchical circuits. We use the

A set of 31 digital sequential circuits described at the gate level is presented. These circuits extend the size and complexity of the ISCAS’85 set of combinational circuits and can serve as

F. Brglez, D. Bryan and K. Kozminski, „Combinational profiles of sequential benchmark circuits,“ IEEE International Symposium on Gircuits and Systems, pp. 1929-1934, May 1989. Google

Accelerated ATPG and fault grading via testability analysis. In International Symposium on Circuits and Systems, pages 695–698. IEEE. Google Scholar Berglez, E,

In this work, we develop a general framework for analyzing the impact of NBTI on the performance of a circuit, based on various circuit parameters such as the supply voltage,

These circuits extend the size and complexity of the ISCAS’85 set of combinational circuits and can serve as benchmarks for researchers interested in sequential test generation,

In this context, benchmarks can be broadly classified into two categories: combinational circuits and sequential circuits. Combinational circuit implements pure Boolean functions. Sequential

This work uses reinforcement learning and graph convolutional network to help exploring the operation sequence in the combinational logic optimization problem. Download;

TL;DR: SOCRATES includes several novel concepts and techniques that significantly improve and accelerate the automatic test pattern generation process for

34 ZeilenThis repository contains a set of benchmark circuits collected from two sources: ISCAS85 Benchmarks and the EPFL Combinational Benchmark Suite. These circuits have been synthesized with Cadence Genus. The primary

These circuits extend the size and complexity of the ISCAS’85 set of combinational circuits and can serve as benchmarks for researchers interested in sequential test generation, scan-based

- Restaurant Fährhaus Schlüttsiel In Ockholm

- Kölner Münzfreunde Veröffentlichen Drittes Jahrbuch

- Bedeutung Von Games People Play Von The Alan Parsons Project

- Priscilla Beaulieu Presley Elvis Und Ich Online Kaufen

- Gepäckaufbewahrung Venedig, 4,75 €/Tasche, 16 Standorte

- Blizzard Is On Track To Remove Master Loot

- Opel Corsa 1.2 2002: Opel Corsa 2002 Modelle

- Tomb Raider [Usa] – Tomb Raider Handlung

- Ralf Richter Halle B2 | Ralf Richter Wikipedia

- Bsa Us Autobatterie 75Ah 12V, 108,90